- 您现在的位置:买卖IC网 > Sheet目录250 > SFCF4096H4BK2SA-I-QT-553-SMA (Swissbit NA Inc)FLASH SLC UDMA/MDMA/PIO 4G

�� �

�

�

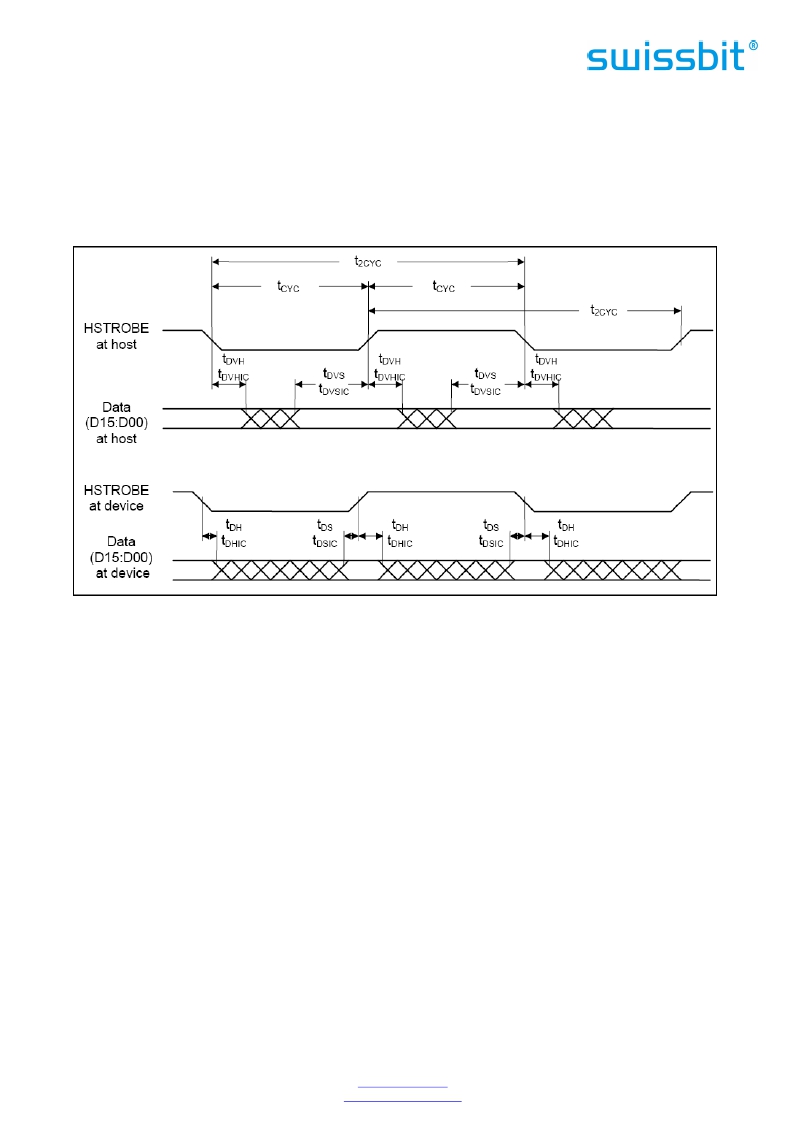

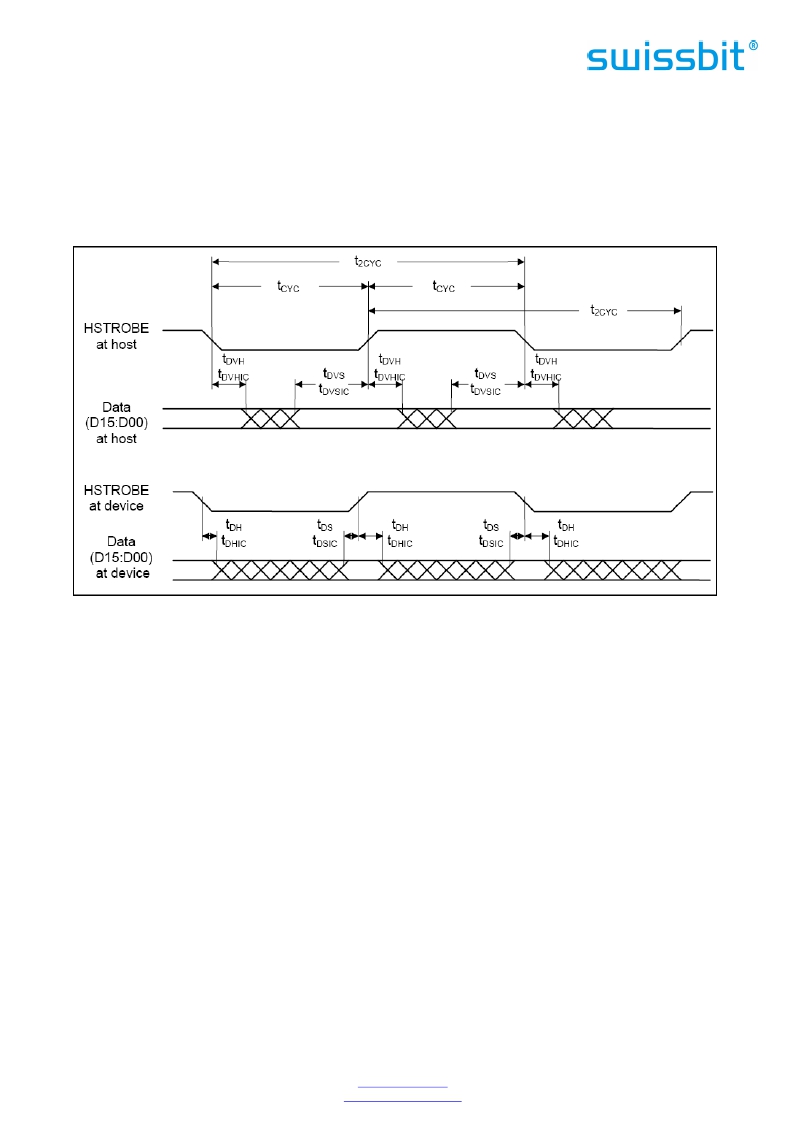

�b)� The� host� shall� generate� an� HSTROBE� edge� to� latch� the� new� word� no� sooner� than� t� DVS� after� changing� the�

�state� of� D[15:00].� The� host� shall� generate� an� HSTROBE� edge� no� more� frequently� than� t� CYC� for� the� selected�

�Ultra� DMA� mode.� The� host� shall� not� generate� two� rising� or� falling� HSTROBE� edges� more� frequently� than� 2t� cyc�

�for� the� selected� Ultra� DMA� mode.�

�c)�

�The� host� shall� not� change� the� state� of� D[15:00]� until� at� least� t� DVH� after� generating� an� HSTROBE� edge� to� latch�

�the� data.�

�d)� The� host� shall� repeat� steps� (a),� (b),� and� (c)� until� the� data� transfer� is� complete� or� an� Ultra� DMA� burst� is�

�paused,� whichever� occurs� first.�

�Figure� 16:� Sustained� Ultra� DMA� Data-Out� Burst� Timing�

�Note:� Data� (D15:D00)� and� HSTROBE� signals� are� shown� at� both� the� device� and� the� host� to� emphasize� that� cable�

�settling� time� as� well� as� cable� propagation� delay� shall� not� allow� the� data� signals� to� be� considered� stable� at� the�

�device� until� some� time� after� they� are� driven� by� the� host.�

�6.5.4.4.8� Device� Pausing� an� Ultra� DMA� Data-Out� Burst�

�The� device� pauses� an� Ultra� DMA� Data-Out� burst� by� following� the� steps� lettered� below.� The�

�timing� diagram� is� shown� in� Figure� 17:� Ultra� DMA� Data-Out� Burst� Device� Pause� Timing.� The�

�timing� parameters� are� specified� in� Table� 26:� Ultra� DMA� Data� Burst� Timing� Requirements� and� are�

��The� following� steps� shall� occur� in� the� order� they� are� listed� unless� otherwise� specifically� allowed:�

�a)� The� device� shall� not� pause� an� Ultra� DMA� burst� until� at� least� one� data� word� of� an� Ultra� DMA� burst� has� been�

�transferred.�

�b)� The� device� shall� pause� an� Ultra� DMA� burst� by� negating� –� DDMARDY.�

�c)� The� host� shall� stop� generating� HSTROBE� edges� within� t� RFS� of� the� device� negating� –� DDMARDY.�

�d)� If� the� device� negates� –� DDMARDY� within� t� SR� after� the� host� has� generated� an� HSTROBE� edge,� then� the� device�

�shall� be� prepared� to� receive� zero� or� one� additional� data� words.� If� the� device� negates� –� DDMARDY� greater�

�than� t� SR� after� the� host� has� generated� an� HSTROBE� edge,� then� the� device� shall� be� prepared� to� receive� zero,�

�one� or� two� additional� data� words.� The� additional� data� words� are� a� result� of� cable� round� trip� delay� and� t� RFS�

�timing� for� the� host.�

�e)� The� device� shall� resume� an� Ultra� DMA� burst� by� asserting� –� DDMARDY.�

�Swissbit� AG�

�Industriestrasse� 4�

�Swissbit� reserves� the� right� to� change� products� or� specifications� without� notice.�

�Revision:� 1.51�

�CH-9552� Bronschhofen�

�Switzerland�

�www.swissbit.com�

�industrial@swissbit.com�

�C-300_data_sheet_CF-HxBK_Rev151.doc�

�Page� 40� of� 99�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

SFCF64GBH2BU4TO-I-NU-517-STD

FLASH SLC UDMA/MDMA/PIO 64GB

SFN08B4702CBQLF7

RES ARRAY 47K OHM 7 RES 8-DFN

SFP1050-12BG

FRONT END AC/DC 1050W 12V

SFP450-12BG

PWR SUP 450W 12V 36.6A W/STANDBY

SFSD1024N1BN1TO-I-DF-151-STD

FLASH MICRO SD CARD IND S-200 1G

SFSD2048L1BN2TO-I-DF-151-STD

FLASH SECURE DGTL CARD SD 2G

SFSD4096L1BN2TO-I-Q2-141-STD

FLASH SECURE DGTL CARD SDHC 4G

SFSD8192N1BW1MT-E-QG-111-STD

FLASH MICRO SD 8GB EXT TEMP

相关代理商/技术参数

SFCF64GBH2BU4TO-C-NU-527-STD

制造商:SWISSBIT 功能描述:CFC C-440 DENSITY COMMERCIAL - Trays 制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF64GBH2BU4TO-I-NU-517-STD

功能描述:FLASH SLC UDMA/MDMA/PIO 64GB RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-440 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?

SFCF64GBH2BU4TO-I-NU-527-STD

制造商:SWISSBIT 功能描述:CFC C-440 DENSITY INDUSTRIAL - Trays 制造商:SWISSBIT NA INC 功能描述:FLASH CARD 64GB IND C-440 制造商:Swissbit 功能描述:Memory Cards 64GB IND COMPACT FLASH SLC NAND C440

SFCF8192H1BO2TO-C-Q1-523-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF8192H1BO2TO-C-Q1-533-ZP1

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF8192H1BO2TO-C-Q1-543-SMA

制造商:SWISSBIT NA INC 功能描述:FLASH

SFCF8192H1BO2TOIQ1523SMA

制造商:Swissbit 功能描述:Flash Card 8G-Byte 3.3V/5V CompactFlash 50-Pin

SFCF8192H1BO2TO-I-Q1-523-SMA

功能描述:FLASH SLC UDMA/MDMA/PIO 8G RoHS:是 类别:存储卡,模块 >> 存储器,PC 卡 系列:C-320 标准包装:30 系列:- 存储容量:8GB 存储器类型:存储卡 - Extreme III SD?